MOS管的基本性質

MOS管,即場效應管,四端器件,S、D、G、B四個端口可以實現開和關的邏輯狀態,進而實現基本的邏輯門。

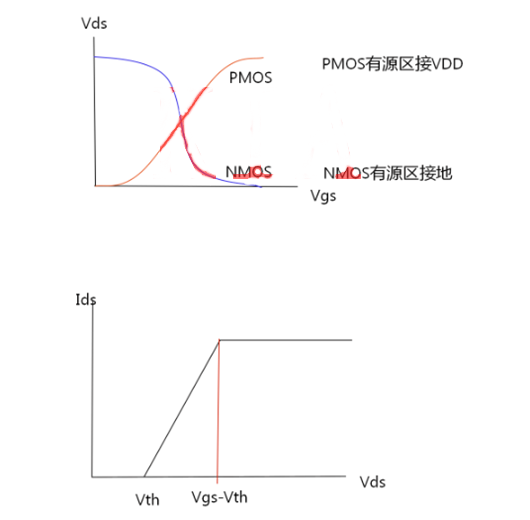

NMOS和PMOS具有明顯的對偶特性:NMOS高電平打開(默認為增強型,使用的是硅柵自對準工藝,耗盡型器件這里不涉及),PMOS低電平打開。在忽略方向的情況下,采用共S極接法,有如下特性:

第一張圖是Vds隨Vgs變化的情況,用于描述開關特性。后面的邏輯分析一般基于這個原理。

第二張圖是Ids隨Vds變化的情況的簡圖,用于描述MOS的靜態特性。

MOS的靜態特性由兩個區域決定:線性區和飽和區。前者一般是動態功耗的主要原因,后者是靜態電壓擺幅的決定因素。

線性區有:Id=μCoxW/L[(Vgs-Vth)Vds-1/2Vds^2]

飽和區有:Id=1/2μCoxW/L(Vgs-Vth)^2

后面的MOS器件一般基于這兩個區域的電學特性來分析總體的電學特性。電壓擺幅、面積、噪聲容限、功耗、延時基本上都是源自這個區域的原理。

TG及其改進

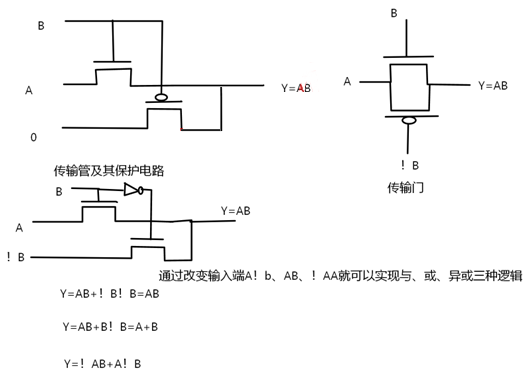

(1)傳輸管邏輯

傳輸管和傳輸門的區別在于否是有全電壓擺幅,其實現的邏輯功能是一致的。

可以看到,傳輸管實現邏輯的關系還是串聯和并聯,并且串聯為與,并聯為或,需要使用保護電路防止懸空。輸出的邏輯與輸入的信號有關,這可以作為可編程的電路的單元。

(2)TG邏輯的改進

TG邏輯的改進還是專注于去除PMOS。根據反向輸入的NMOS等于PMOS的思路,如上圖3中的結構,可以將PMOS替代。可以看到的傳輸管不能無損傳輸,信號需要使用反相器恢復穩定。

動態電路

靜態電路需要保持上拉和下拉電路一直互斥,存在動態損耗。

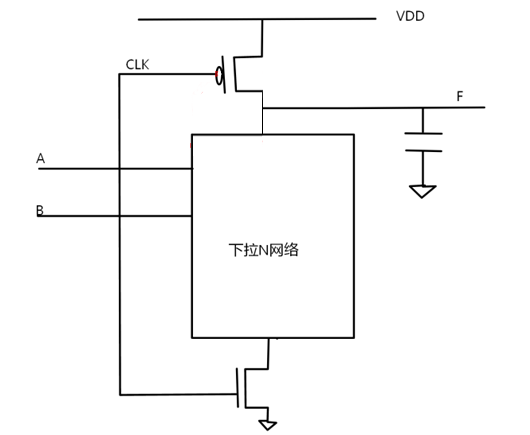

動態電路的思路則是使用時鐘信號保證上下電路互斥,這樣只需要一個網絡就可以實現目標功能。圖中是下拉N網絡的電路,還可以使用上拉P網絡實現,兩者的級聯要求正好對偶,可以間隔連接。這就是動態電路的級聯的形式一PN連接。

還有一種方式就是使用多米諾電路,就是在同N或者同P之間使用反相器保證動態電路預充正確。

接下來說明動態電路的工作方式:

預充-求值

在CLK=0時,P導通,輸出預充到1;

在CLK=1時,N導通,讀取N網絡的導通狀態,決定求值為0或者1;

一次預充求值完成后即實現邏輯輸出。

問題:求值時輸入不能發生改變,否則會出現邏輯x,這意味著動態電路多與時序電路聯合使用,構成流水線。

問題:電容存儲電荷實現電平存在損耗,需要CLK不斷刷新。

動態電路的優化:

第一級動態電路CLK需要P和N兩個MOS管,對于第二級動態電路,預充時已知某個信號為0(多米諾為0,PN連接為1),如果輸入邏輯為與或者可以保證網絡關閉,則可以節約一個網絡控制MOS管。

組合邏輯分析

(1)電壓擺幅

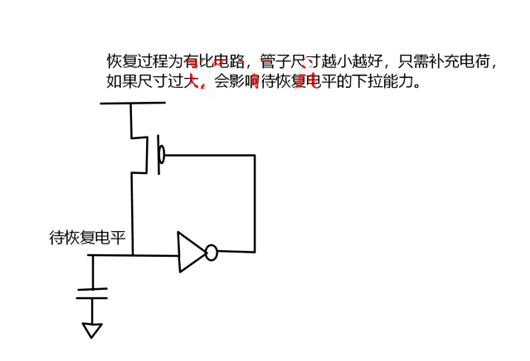

電平需要能夠維持在L1和L0兩個狀態區間內,一旦混亂,就會出現邏輯錯誤。一般來說,可以使用電平恢復電路維持電壓(一個反相器與PMOS構成的電平恢復)。對于長的邏輯鏈,需要加入BUFF來維持電壓(這點在傳輸管中尤為重要)。

(2)邏輯延時

這部分是分析組合電路的延時的,采用的反相器為標準的估算方法(軟件可以實測,但是設計時需要估值),專業詞匯叫邏輯努力。

標準反相器鏈的延時T=tp0+tp0*f,其中tp0是空載延時,f是扇出。f=Cout/Cin,在同尺寸的反相器串聯時,f=1,并聯時f=N,N為下一級并聯的個數。常用術語FO4即是扇出為4的設計。對于不同的反相器,則需要使用具體的計算得到比例。反相器鏈采用f=F^(1/N)的優化規則優化。

基于反相器鏈,可以推導CMOS門鏈的延時:反相器常用P:N的W/L為2:1(綜合面積,速度,噪聲,功耗的考慮值),以此為基準可以推出同等最優尺寸的與非門尺寸為2:2:2:2,或非門尺寸為4:4:1:1,推算原則就是串聯翻倍,并聯不變的最優尺寸等效規則。

然后是CMOS門的延時:d=p+gh,p為基準延時tp0的倍數,g為電學努力,h為邏輯努力。以與非門為例,得出下面的參數:p=2(等效兩個理想反相器),g=4/3(A=2+2,B=2+2),h=Cout/Cin(單鏈,如果有分支,加上b這個參數,即下一級的負載數)。

優化的方法也是一樣的,使得f=F^(1/N),即可實現最優延時。f=gh,F=GBH,大寫即為連乘的小寫。

鎖存器

限于篇幅,這里不再再畫圖,大致解釋一下鎖存器的結構:類似一個時鐘控制開關(一般使用傳輸門作為開關),時鐘打開開關時讀取數據,關閉時鎖存數據。通過時鐘信號實現輸出數據在一段時間內(理想情況下為半個周期)與輸入隔離。

觸發器

由兩個鎖存器和中間一個存儲單元(一般是首尾相連的反相器)組成。鎖存器的鎖存時間相反,輸入端鎖存器打開時存入數據,鎖存時讀出數據。與鎖存器整個時鐘周期都在鎖存依靠電平不同,觸發器依靠時鐘的上升和下降實現數據的存儲,且輸出整個時鐘周期不發生改變。

時序邏輯分析

建立時間:數據需要提前于時鐘沿的時間,保持時間:數據需要在時鐘沿到來后保持的時間。傳輸時間:數據從存儲單元傳輸到輸出所需的時間。

具體的分析是復雜的,但是基本的原理是清晰的。建立時間是為了保證數據能夠存入存儲單元。保持時間是保證數據能度過時鐘觸發所需的延時。傳輸時間是保證存儲單元數據能夠傳輸到輸出。

具體的時序分析是很復雜的,需要考慮許多參數,如時鐘的抖動和歪斜。一般這些參數都是計算好的,使用者只需根據計算值設計相應的滿足條件即可。基本的修改方法是:對于關鍵路徑,建立時間不足降低時鐘頻率,保持時間不足加BUFF。

至于如何修改建立時間和保持時間,那是電路結構的問題,需要設計更加合理的電路。常用的電路結構為C^2MOS結構,即將時鐘和反相器組合成的MOS時序電路,有興趣可以查一下。這個結構可以和多米諾組成流水線的結構。

功能模塊

加法器、乘法器、多路選擇器、移位寄存器、存儲器等具有特定邏輯功能的電路所需的是邏輯設計,學習過數字電路的都不會陌生(存儲器就是基于存儲單元的讀寫DRAM和基于電容的SRAM),這里已經到了module層次了。

這個層次的設計已經可以使用verilog快捷的實現了。優化也可以基于verilog來調試優化每個門的位置和數量。

總結

本文從MOS管開始,介紹了MOS,傳輸管TG的原理、動態電路的結構、組合邏輯延時的分析,簡略地介紹了鎖存器、觸發器及時序電路的分析,聯系到了模塊層次的數字電路設計。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹